## HARMONIC TUNED PAs DESIGN CRITERIA

Paolo Colantonio\*, Franco Giannini\*, Giorgio Leuzzi<sup>†</sup> and Ernesto Limiti\*

\* Dip. Ingegneria Elettronica, Università di Roma Tor Vergata, V. Politecnico 1, 00133 Roma - Italy

+ Dip. Ingegneria Elettrica, Università di L'Aquila, Poggio di Roio, L'Aquila - Italy

**Abstract** — High efficiency power amplifier design criteria imply the synthesis of input and output networks with particular care on their harmonic behavior. In this paper, a simplified approach to clarify the relevance of such terminations is presented. In particular, design criteria to improve efficiency for high frequency application will be discussed. Finally, to validate the proposed analysis comparison between realised amplifiers are shown.

### I. INTRODUCTION

In high efficiency Power Amplifier (PA) design, a crucial step is in the synthesis of both the input and output networks, accounting not only for fundamental load impedance but also for their harmonic behavior [1,3]. Nevertheless, the role of the harmonic terminations is not yet completely understood, especially for the input network, generally resulting in experimental considerations rather than in design criteria. Moreover, the design of the harmonic terminations becomes very important when the operating frequency increase, therefore limiting the number of harmonics that can be successfully controlled. The aim of this contribution is to infer some useful criteria for the design of input and output networks of high efficiency and high frequency power amplifiers.

### II. HIGH EFFICIENCY DESIGN CRITERIA

Starting from simple power balance considerations, the following expression for the drain efficiency can be derived

$$\eta = \frac{P_{out,f}}{P_{dc}} = \frac{P_{out,f}}{P_{diss} + P_{out,f} + \sum_{n>1} P_{out,nf}} \quad (1)$$

where  $P_{out,nf}$  ( $n \geq 1$ ) is the output power delivered from the active device to the output network, at all the harmonic frequency components, while  $P_{diss}$  is the dissipated power on the device itself. Thus, to maximize drain efficiency it is necessary to satisfy one of the two following equivalent conditions: maximize the fundamental output power  $P_{out,f}$  or minimize both dissipated power on the device ( $P_{diss}$ ) and the output harmonic terminations ( $P_{out,nf}$ ,  $n > 1$ ). It is to note that the minimization of dissipated power only leads to sub-optimum results. To infer useful design criteria, even if the two condition are equivalent, it is easier to manage the former instead of the latter, requiring more parameters. Assuming in fact the active device acting as a voltage-controlled current source, at least while operated in its active region,  $P_{out,f}$  maximization corresponds to the

maximization of the fundamental drain voltage component, with the constraint that the resulting voltage waveform has to be physically consistent. In this way, it is possible to split the load networks design criteria; the input network will *control* the current generating mechanisms, while output network will *maximize* fundamental output power  $P_{out,f}$ . If a periodic steady state is assumed, the drain current waveform is expressed as:

$$i_{DS}(t) = I_0 + \sum_{n=1}^{\infty} I_n \cdot \cos(n\omega t) \quad (2)$$

while the drain voltage has to account for the practical limitations due both to the device intrinsic capacitive behavior and increase in circuit complexity (compared with minor benefits), practically limiting the output harmonic termination control up to 3f. The drain voltage waveform is therefore expressed as:

$$v_{ds}(t) = V_{DD} - V_1 \cdot [\cos(\omega t) + k_2 \cdot \cos(2\omega t) + k_3 \cdot \cos(3\omega t)] \quad (3)$$

$$\text{where } k_2 = \frac{V_2}{V_1}, \quad k_3 = \frac{V_3}{V_1} \quad (4)$$

and the voltage and current harmonic components are related by the output harmonic terminations (assumed resistive for simplicity)

$$R_{L,nf} = \frac{V_n}{I_n} \quad (5)$$

In this simplified analysis, the effect of the active device drain to source internal resistance  $R_{ds}$ , acting as an upper limit for the load resistance feasible values, has been neglected. Assuming an imposed drain current (i.e. fixed  $I_n$  components), the problem of maximizing  $\eta$  is transformed in the selection of  $k_2$  and  $k_3$  values maximizing  $V_1$ , with the boundary condition  $0 \leq v_{ds}(t) \leq V_{BD}$  where  $V_{BD}$  is the device breakdown voltage. The problem has been managed in the past [4], and the results are summarized in Table 1.

TABLE I

RESULTS OBTAINABLE WITH DIFFERENT HARMONIC CONTROL

| Controlled frequencies |                           | $k_2$ | $k_3$ | $\delta$ | $\beta$ | Achievable $V_1$    |

|------------------------|---------------------------|-------|-------|----------|---------|---------------------|

| f                      | Tuned Load                | 0     | 0     | 1        | 1       | $V_{DD}$            |

| f, 3f                  | Class F                   | 0     | -0.17 | 1.15     | 1       | $1.15 \cdot V_{DD}$ |

| f, 2f                  | 2 <sup>nd</sup> h. tuning | -0.35 | 0     | 1.41     | 1.91    | $1.41 \cdot V_{DD}$ |

| f, 2f, 3f              | Class FG                  | -0.55 | 0.17  | 1.62     | 2.8     | $1.62 \cdot V_{DD}$ |

In this table, *Voltage Gain Function*  $\delta$  relates the fundamental drain voltage amplitude  $V_1$ , obtainable by proper harmonic terminations (i.e.  $(k_2, k_3)$  pair), to the bias voltage  $V_{DD}$ , that can be considered as the fundamental amplitude for the unmanipulated approach, i.e. for the Tuned Load (TL) case. The *Voltage Overshoot Function*  $\beta$  quantifies the overshoot phenomena due to the use of even harmonic components. The two figures are defined as:

$$\delta(k_2, k_3) = \frac{V_1}{V_{DD}} \quad \beta(k_2, k_3) = \frac{\max[V_{ds}(t)]}{V_{DD}} \quad (6)$$

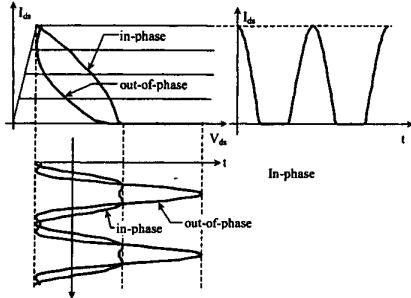

The  $\delta$  function directly gives the improvement on drain efficiency  $\eta$  with respect to the Tuned Load (TL) case. However, the  $\delta$  values have to be considered carefully, not to violate physical constraints. In fact, since drain voltage harmonic components  $V_n$  are generated by the current harmonic ones  $I_n$  through the drain impedances  $R_{L,nf}$  (eqn. (5)), the  $k_2$  and  $k_3$  optimum values must be physically synthesized, i.e. the corresponding impedances  $R_{L,2f}$  and  $R_{L,3f}$  must be positive values.  $I_2$  and  $I_3$  have therefore to satisfy proper phase relationships with respect to  $I_1$  (Table 1, sign of  $k_2$  and  $k_3$ ). Such relationships are very important, since if not fulfilled may lead to detrimental results (Fig.1).

Fig.1:Output load curve for 2<sup>nd</sup> harmonic tuning approach with proper (out-of-phase) or wrong (in-phase) voltage components

Optimum load impedances for the intrinsic drain current source can be determined as

$$R_{L,f} = \delta(k_2, k_3) \cdot \frac{V_{DD}}{I_1} \quad R_{L,nf} = \delta(k_2, k_3) \cdot k_n \cdot \frac{V_{DD}}{I_n} \quad (7)$$

$n = 2, 3$

Thus the harmonic 'output' approach can be useful if the generated drain current waveform allows positive values for  $R_{L,nf}$ , according to eqn (7). In fact, even if there is a power dissipation on such harmonic loads, that could be interpreted as a detrimental phenomena, the fundamental output power is maximized, simultaneously maximizing drain efficiency. It is to note that if the same analysis were applied to minimize the dissipated power, only sub-optimum results could be obtained [5].

This simplified analysis shows that the of the harmonic manipulation approach are related to the output harmonic terminations and to the drain current waveforms. Thus, even if they don't explicitly appear in the previous equations, also the input harmonic terminations become important to control the drain current generation mechanism as noted in [4,6]. To generalize, the following drain current waveform can be considered:

$$i_{DS}(t) = \begin{cases} I_{DD} + A_1 \cdot \left[ \cos(\omega t) + h_2 \cdot \cos(2\omega t) \right] & \text{if } -\frac{\alpha}{2} \leq \omega t \leq \frac{\alpha}{2} \\ 0 & \text{otherwise} \end{cases} \quad (8)$$

where  $\alpha$  is the drain current conduction angle, and  $c$  is the bias percentage defined by

$$I_{DD} = c \cdot I_{max} \quad 0 \leq c \leq 0.5 \quad (9)$$

with  $I_{max}$  maximum achievable drain current, and

$$h_2 = \frac{A_2}{A_1} \quad (10)$$

with  $A_1$  and  $A_2$  related by the transconductance  $g_m$  to the input voltage controlling harmonic components, i.e. to the input network design. Through the appropriate *input* network design, it is possible to realize different  $A_n$  *output* coefficients, obtaining different drain current harmonic components  $I_n$ , to be terminated according to eqn. (7). In this way the effects of the input harmonic terminations are distinguished from those related to the output terminations: the input network is designed to generate the proper  $A_n$  coefficients, while the output network is designed to properly terminate the so-obtained output drain current harmonic components. The analysis has been performed considering  $c$  and  $h_2$  as independent variables with the aim of maximizing the drain efficiency, properly terminating fundamental and second harmonic only, according to the above mentioned statements. In particular, since  $h_2$  is used to control the phase between fundamental ( $I_1$ ) and second ( $I_2$ ) harmonic current components, its range can be limited to negative values only (positive values actually produce in-phase  $I_1$  and  $I_2$  components). Moreover, assuming that the output current waveform reaches its peak value  $I_{max}$ , it is possible to relate the  $A_1$  value and the drain conduction angle  $\alpha$  to the values of  $c$  and  $h_2$ . In fact, defining the function

$$f(c, h_2) = \begin{cases} \frac{c-1}{h_2 + \frac{1}{8h_2}} & h_2 \leq -\frac{1}{4} \\ \frac{1-c}{1+h_2} & -\frac{1}{4} < h_2 \leq 0 \end{cases} \quad (11)$$

the following closed form expressions for  $A_1$  and  $\alpha$  can be derived (details of the analysis are omitted in this paper):

$$A_1 = I_{\max} \cdot f(c, h_2) \quad (12)$$

$$\alpha = 2 \cdot \alpha \cos \left[ -\frac{1}{4h_2} + \frac{1}{4h_2} \sqrt{1 - 8 \frac{h_2 \cdot c}{f(c, h_2)} + 8h_2^2} \right] \quad (13)$$

Current harmonics can be written in closed-form, as functions of  $c$  and  $h_2$ , i.e.:

$$I_n = I_{\max} \cdot g(n, c, h_2) \quad (14)$$

where  $g$  is a function of  $n$  (harmonic index),  $c$  and  $h_2$ . Theoretically achievable drain efficiency for the TL approach, (i.e. short circuiting the output harmonics) is:

$$\eta_{TL}(c, h_2) = \frac{1}{2} \frac{I_1 \cdot V_{DD}}{I_0 \cdot V_{DD}} = \frac{1}{2} \frac{g(1, c, h_2)}{g(0, c, h_2)} \quad (15)$$

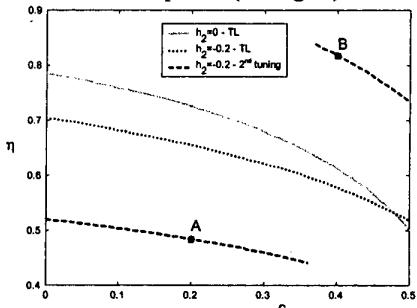

For 2<sup>nd</sup> harmonic tuning design, if  $I_2$  is opposite in phase with  $I_1$ , it is possible to use the output harmonic tuning, according to eqn.(7); otherwise, to avoid 2<sup>nd</sup> harmonic potential detrimental effects, it is better to short the  $I_2$  component and terminate  $I_1$  on the optimum resistive load (TL approach), i.e.  $R_{L,f}$  with  $\delta=1$ . To stress the relevance of phase relationships between harmonic components ( $I_1$  and  $I_2$ ), in Fig.2 the efficiency obtainable assuming  $h_2=-0.2$  and loading the  $I_2$  component with a resistance whose value is determined by the module of eqn (7) (dashed line) is shown and compared to a TL approach with (dotted line) or without input 2<sup>nd</sup> harmonic generation (grey line).

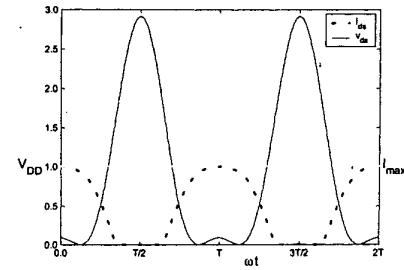

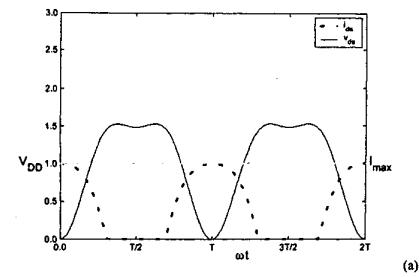

As can be noted, if  $c$  is less than 0.37, the efficiency for a TL approach is higher than the one obtainable by 2<sup>nd</sup> harmonic tuning. In this case it is obvious that the generation of  $h_2$  has been deleterious and it is better to short circuit the  $I_2$  component not to deteriorate drain efficiency (point A). In fact, since  $I_1$  and  $I_2$  are in phase, then the voltage waveform obtainable loading both current components on resistive loads has a lower fundamental component, so decreasing overall efficiency with respect to a TL approach (Fig.3a). On the other hand, if  $c$  is higher than 0.37, 2<sup>nd</sup> harmonic tuning becomes better than a TL approach (point B) since the voltage waveform has an higher fundamental component (see Fig.3b).

Fig.2: Drain efficiency with  $h_2=-0.2$  for a TL approach, i.e. short circuiting  $I_2$  (dotted), adopting a 2<sup>nd</sup> harmonic tuned (dashed) compared with a TL approach with  $h_2=0$  (grey line).

Fig.3: Voltage and Current waveforms corresponding to (a) point A in Fig.2 ( $h_2=-0.2$ ,  $c=0.2$ ) and (b) point B in Fig.2 ( $h_2=-0.2$ ,  $c=0.4$ ).

From this results, it is obvious to conclude that the effects of the harmonic manipulation could be fruitful or not, depending on the harmonic current components phase relationships.

An important comment arises from Fig.2: for a fixed  $h_2$  value (-0.2 in the example), there is a correspondent value for the bias percentage  $c$  ( $\approx 0.36$ ) where the  $I_2$  component vanishes. This point is related to the intermodulation sweet spot location [7].

### III. DESIGN VERIFICATION

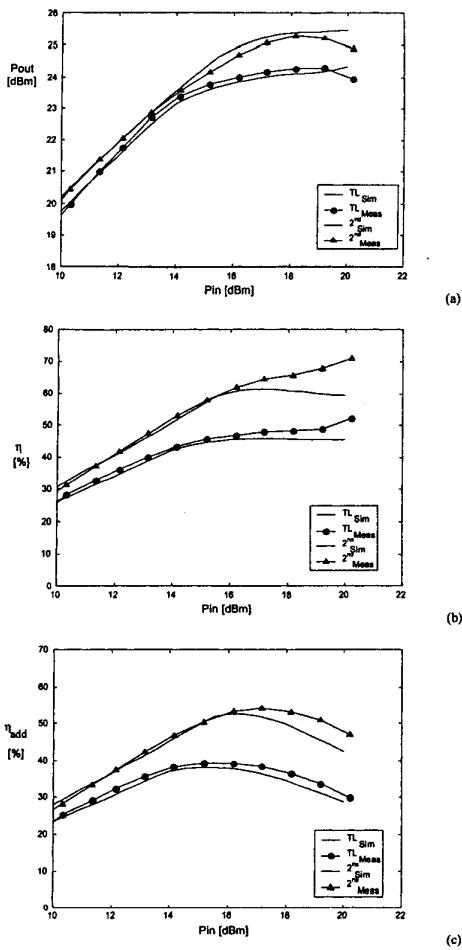

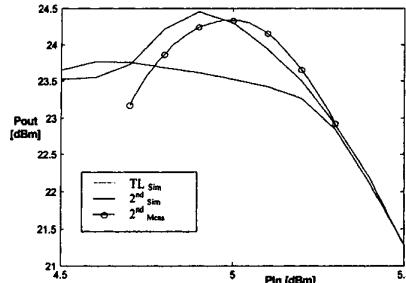

To validate the present approach, two PAs have been designed using a medium power GaAs MESFET ( $0.5 \mu\text{m}$  gate length, 1 mm gate periphery) by AMS. A Class AB bias condition has been selected ( $c \approx 0.26$ ), with  $V_{DD}=5\text{V}$ . The first PA is a TL one, designed as a reference, while the other is a 2<sup>nd</sup> harmonic tuned amplifier. Both the amplifiers have been optimized @5GHz. Simulated and measured performances are reported in Fig.4, while in Table 2 the 1dB compression point performances are shown and compared with the values obtained by the presented simplified analysis, taking into account a  $V_k=1.8\text{V}$ . As it is possible to note, the proposed approach allows the simultaneous increase in output power, large signal gain and efficiency, as contrasted with simpler non-harmonic tuning strategies. In Fig.5 the measured output power of the 2<sup>nd</sup> harmonic tuned PA is plotted as a function of frequency together with simulations and its companion TL

stage, at 2 dB compression. Measured results demonstrate a 10% bandwidth around 5GHz.

Fig.4: Simulated and measured output power (a), drain (b) and power added efficiency (c) for the realized TL and 2<sup>nd</sup> harmonic tuned PAs.

Fig.5: Output power for the 2<sup>nd</sup> harmonic tuned PA (measured and simulated) and for the TL PA, computed at 2 dB compression.

TABLE 2

COMPARISON BETWEEN THEORETICAL, SIMULATED AND MEASURED DRAIN EFFICIENCY AT 1DB COMPRESSION POINT

| $\eta_{TL\_The}$ | $\eta_{TL\_Sim}$ | $\eta_{TL\_Meas}$ | $\eta_{2nd\_The}$ | $\eta_{2nd\_Sim}$ | $\eta_{2nd\_Meas}$ |

|------------------|------------------|-------------------|-------------------|-------------------|--------------------|

| 44.3             | 43.4             | 44.5              | 55.1              | 53.7              | 55.3               |

The good agreement between the results predicted by the proposed simplified approach and measured performances validates the suggested strategy.

#### IV. CONCLUSIONS

In this paper, starting from the basic power balance equation, a simplified analysis has been presented to obtain useful design criteria for both input and output networks loading of high efficiency PAs. In particular, it has been demonstrated that the output network has to be designed to maximize the fundamental output power through proper harmonic load terminations. Moreover, the relevance of the input harmonic terminations to generate output drain harmonic components with proper phase relationships, has been stressed utilizing closed form expression. The proposed approach has been validated comparing the theoretical results with measured data.

#### REFERENCES

- [1] M.Maeda et al., "Source Second-Harmonic Control for High Efficiency Power Amplifiers," IEEE Transactions on Microwave Theory and Techniques, Vol. MTT-43, N°12, December 1995, pp.2952-2958.

- [2] S.R.Mazumder, A.Azizi, F.E.Gardioli, "Improvement of a Class-C Transistor Power Amplifier by Second-Harmonic Tuning," IEEE Transactions on Microwave Theory and Techniques, Vol. MTT-27, N°5, May 1979, pp.430-433.

- [3] S. Watanabe et al., "Simulation and Experimental Results of Source Harmonic Tuning on Linearity of Power GaAs FET Under Class AB Operation," 1996 IEEE MTT-S Symposium Digest, pp. 1771-1777.

- [4] P.Colantonio, F.Giannini, G.Leuzzi, E.Limiti, "Multi Harmonic Manipulation for Highly Efficient Microwave Power Amplifiers," Int. Journal on RF and Microwave CAE, Vol.11, N°6, Nov. 2001, pp. 366-384.

- [5] F.H.Raab, "Class-F Power Amplifiers with Maximally Flat Waveforms," IEEE MTT Transactions, Vol.MTT-45, N°11, November 1997, pp.2007-2012.

- [6] P.Colantonio, F.Giannini, G.Leuzzi, E.Limiti, "High Efficiency Low-Voltage Power Amplifier Design by Second Harmonic Manipulation," Int. Journal on RF and Microwave CAE, Vol.10, N°1, January 2000, pp.19-32.

- [7] M.Moazzam, C.S.Aitchison, "A Low Third Order IMD Amplifier With Harmonic Feedback Circuitry," 1996 IEEE MTT-S Symposium Digest, pp.827-830.